Будьте завжди в курсі!

Дізнавайтесь про новітні розробки першими

Новини

Всі новини

17 Жовтня 2023

Нова 4K USB-камера Kurokesu

4 Вересня 2023

FPD-Link III та GMSL2 - нові можливості камер Alvium

3 Квітня 2023

Нова світлодіодна УФ-піч від UWAVE

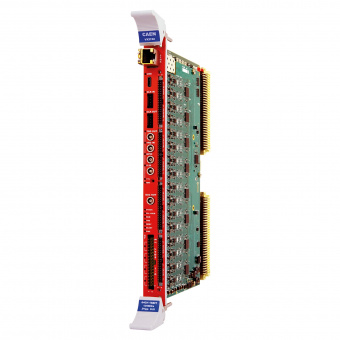

CAEN VX2740 аналого-цифровий перетворювач 64 ch 16 bit (125МS/s)

Новинка

64-канальний 16-бітний (125МС/с) аналого-цифровий перетворювач CAEN VX2740

Детальніше

Під замовлення

-

+

Технічний довідник

- Опис

- Задати питання

-

64-канальний 16-бітний (125МС/с) аналого-цифровий перетворювач CAEN VX2740

64 Channel 16 bit 125 MS/s Digitizer

Особливості:

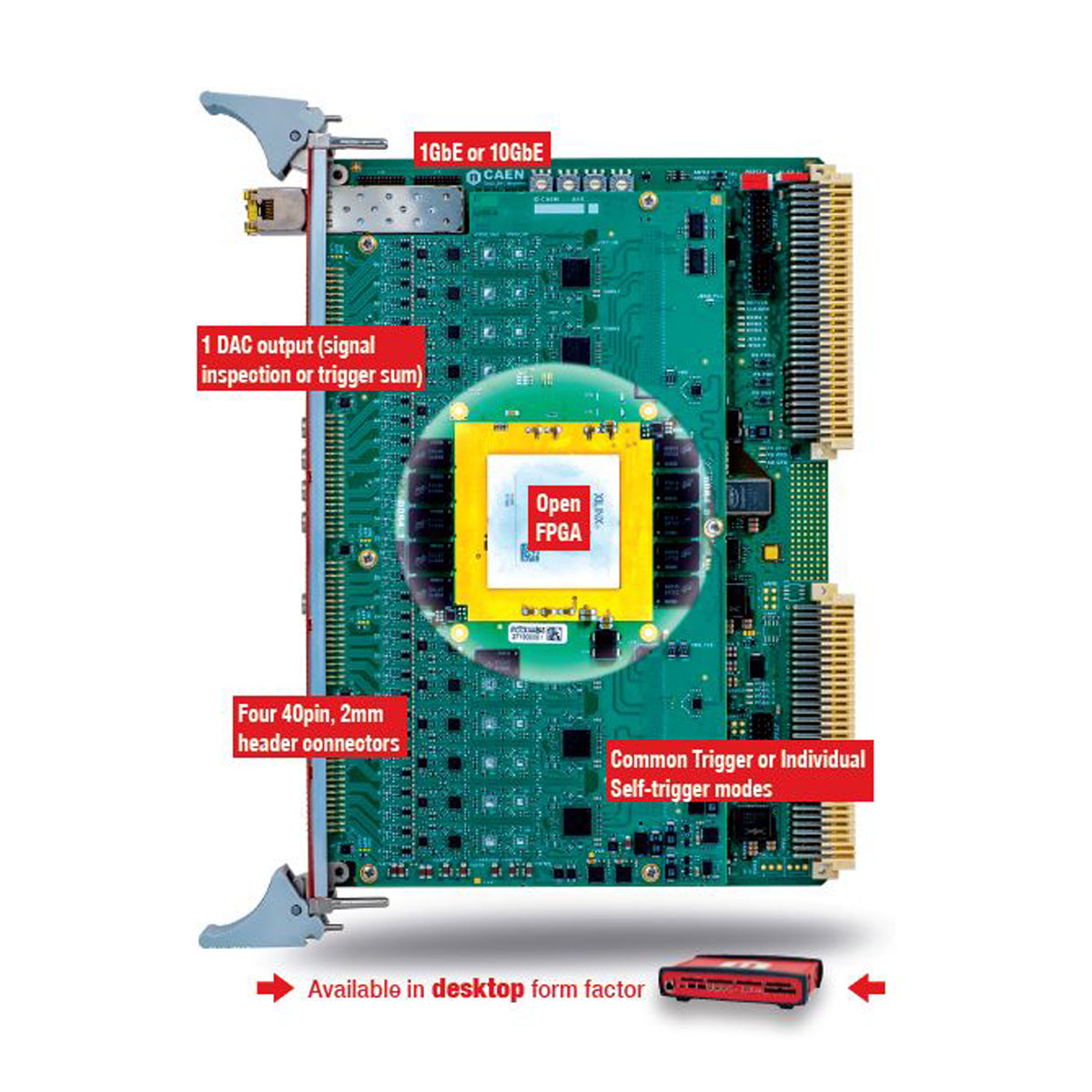

- 16 біт при 125 Мс/с АЦП

- 64 аналогових входи, диференційних або несиметричних, на чотирьох 2 мм 40-контактних роз'ємах

- Діапазон входу 2Vpp, фіксоване аналогове підсилення x1

- Також доступний настільний варіант DT2740

- Широкий спектр застосувань (від фізики нейтрино та темної матерії до ядерної фізики та фізики частинок до спектроскопічної візуалізації)

- Підходить для сигналів від напівпровідникових детекторів у поєднанні з CSP (Si, HPGe) або сцинтиляторів у поєднанні з PMT (NaI, CsI)

- Вибір вбудованого програмного забезпечення для різних режимів збору даних:

- Режим Scope (одночасне отримання необробленої форми сигналу на загальному запуску)

- Режим DPP-PHA (отримання висоти імпульсу та часу на незалежних самозапусках каналів)

- Схильність до інших запланованих алгоритмів: QDC, PSD, CFD, DAW, ZLE тощо.

- Можливість синхронізації з кількома платами та побудови системи

- Повністю програмовані входи/виходи передньої панелі (4 LEMO TTL/NIM і 16 LVDS)

- Спеціальний 14-бітний вихід ЦАП 125 МБ/с (LEMO) для перевірки сигналу, генерування імпульсів, мажоритарного рівня

- 2,5 Гб загальної пам'яті для збору даних (DDR4)

- Вбудований Zynq® UltraScale +™ MPSoC з інтеграцією процесора на основі Arm® під керуванням Linux®

- Багатоінтерфейсний: USB-3.0 та 1/10 GbE або оптичний канал CONET (перемикається на одній панелі)

- Повністю підтримується програмним забезпеченням для зчитування CoMPASS і WaveDump2 (підтримка ComPASS незабаром)

- SDK для вбудованого Arm та host PC

- Відкрита архітектура FPGA для налаштування алгоритму аналізу імпульсів

Загальні:

Виконання:

- VME64X 6U шириною 1 блок

- VX2740/V2740: 642 г

- VX2740В/V2740В: 642 г

Канали:

- 64 канали

- Диференційні на версії 2740

- Несиметричні у версіях 2740B

- Чотири 2 мм 40-контактні роз'єми

- Доступні вхідні адаптери

- 50 МГц

- 50 Ом несиметричний

- Диференційний 100 Ом

- 2 Vpp

- Індивідуальне зміщення регулюється в діапазоні ±1,25 В

Роздільна здатність:

- 16 біт

- 125 мс/с (одночасно на кожному вході)

- ENOB:11.7 (тип.)

- RMS:3,9 LSB (≃ 120 мкВ) типове RMS

CLK-IN

Дві диференційні пари:

- CLK: опорний тактовий сигнал

- SYNC: сигнал синхронізації (старт/зупинка, T0 тощо)

- LVDS, ECL, PECL, LVPECL, CML з підключенням до змінного струму

- Zdiff = 100 Ом

- 2,54 мм 4-контактний штекерний роз'єм AMPMODU Mod II

- Такі ж функції, як і CLK-IN

- Послідовний ланцюжок у синхронізації з кількома платами

- LVDS

- 2,54 мм 4-контактний штекерний роз'єм AMPMODU Mod II

- 16 диференційних пар

- Програмний ввід-вивід (окремі виходи самозапуску, перевірка запуску, закриття, зайнятість , запуск, зупинка, вхід шаблонів тощо)

- LVDS

- Zdiff = 100 Ом (якщо встановлено як входи)

- 2,54 мм 34-контактний штекерний роз'єм AMPMODU Mod II

- Входи/виходи загального призначення

- Програмне забезпечення, яке можна програмувати (запуск, відкриття, закриття, зайнятість тощо)

- Несиметричний TTL/NIM

- TRG-IN/S-IN з внутрішнім кінцевим навантаженням 50 Ом (Zin = 50 Ом)

- TRG-OUT вимагає Rt = 50 Ом

- GPIO як вхід повинен бути з кінцевим навантаженням 50 Ом

- GPIO як вихід TTL вимагає Rt = 50 Ом

- GPIO як вихід NIM вимагає Rt = 50 Ом або 25 Ом

- LEMO 00 штекерний роз'єм

- Вихід ЦАП для перевірки сигналу, генерації імпульсів, мажоритарний рівень

- 14-бітний цифро-аналоговий перетворювач (ЦАП)

- Швидкість оновлення 125 мс/с

- ±1 В при навантаженні 50 Ом; ±2 В при навантаженні hi-Z Вихідний діапазон

- LEMO 00 штекерний роз'єм

- Загальний розмір пам'яті DDR4 2,5 ГБ (20,971 MS/ch), розділений на декілька буферів

- Максимальна тривалість запису: ≃ 168 мс при 125 мс/с (загальний розмір пам’яті, поділений на 2)*

* Значення, віднесене до внутрішнього програмного забезпечення Scope (допускаються мінімум два буфери)

Режими запуску:

- Загальний: всі канали отримують одночасно з запуском (програмне забезпечення, зовнішнє або логічне поєднання самозапусків)

- Індивідуальний: кожен канал набуває самостійно зі своїм самозапуском

- Корельований: індивідуальний самозапуск кожного каналу перевіряється логікою збігу/антизбігу між іншими самозапусками та/або зовнішніми входами/виходами

Такт поширення:

- Типова частота 62,5 МГц, розподілена ланцюжком через CLK-IN/CLK-OUT або розгалуженням на CLK-IN.

- Можлива підтримка користувальницьких частот

- Послідовний ланцюг або розгалуженням на CLK-IN/CLK-OUT або NIM/TTL, LVDS I/Os

- Логіка Зайнята/закрита на входах/виходах LVDS або NIM/TTL для синхронізації побудови подій

- Zero з входу START або S-IN

- Роздільна здатність: 8 нс

- Діапазон лічильника: 48 біт

- Повний діапазон: ~625 год

- TRG-IN/TRG-OUT NIM/TTL LEMO I/Os (загальний запуск) або LVDS I/Os (загальний або індивідуальний запуск)

Внутрішнє програмне забезпечення, що зберігається у вбудованій флеш-пам’яті, і перезавантажується в реальному часі за допомогою веб-інтерфейсу

Внутрішнє програмне забезпечення DPP:

Реалізує алгоритм цифрової обробки імпульсів:

- DPP-PHA: Аналіз висоти імпульсу

- DPP-QDC: Накопичення заряду

- DPP-PSD: Розрізнення форми імпульсу

- DPP-ZLE: Кодування нульової довжини

- DPP-DAW: Вікно динамічного збору даних

- Внутрішнє програмне забезпечення для запису сигналу

Будь-яке підтримуване внутрішнє програмне забезпечення можна завантажити через веб-інтерфейс (як різні типи внутрішнього програмного забезпечення, так і оновлені версії одного внутрішнього програмного забезпечення)

FPGA:

- Багатопроцесорна система на кристалі Xilinx Zynq UltraScale+. XCZU19EG

- Система обробки на базі чотириядерного Arm з 2 ГБ пам'яті DDR4 при 2400 MT/s (вбудована ОС Linux)

- Програмована логіка з більш ніж 1100 000 комірок системної логіки та пам’яттю 80 Мбіт

- Шаблон для користувача області : загальний запуск, одночасний запис сигналу на 64 каналах керування. Налаштування логіки запуску та хвильової обробки

- Шаблон DPP користувача: індивідуальний запуск і керування залученням каналів. Налаштування алгоритму DPP, логіки запуску та інформації про подію

Optical Link (необов'язково)

- Запатентований протокол CONET, CAEN

- Роз'єм Type-C

- Версія USB 3.0

- Швидкість передачі до 280 МБ/с

- Роз'єм SFP+ для 1/10 GbE мідного (RJ-45) або оптичного зв'язку (50/125 мкм OM2 або OM3 волокно)

- TCP-IP стек реалізований у вбудованому Arm

- Швидкість передачі до 110 МБ/с при 1Г

Зчитування SW:

- Програмне забезпечення для спектроскопії ComPASS (лише для DPP)

- WaveDump2 (лише для внутрішнього програмного забезпечення Scope)

- Бібліотеки C загального призначення з демонстраційними зразками для ПК з Windows® і Linux® і вбудованим процесором Arm

Управління внутрішнім програмним забезпеченням (наприклад, оновлення та вибір внутрішнього програмного забезпечення на льоту), інформація про плату, конфігурація PLL та Ethernet, моніторинг стану плати

Вимоги до потужності:

VX2740

+12В

0,9 А(тип.)

+5В

3,6 А(тип.)

+3,3В

4,4 А(тип.)

-

Ви можете надіслати питання щодо продукції та роботи компанії