Digital based DAQ are now a well established technique for the readout of both simple and complex experiments. The flexibility and multipurpose capability offered by this approach make it an ideal solution for the researchers needs. CAEN followed this digital revolution since the beginning and can now offer a wide selection of digitizers that can be used with a variety of detectors in different applications.

# Waveform Digitizers

Digitizer Families Waveform Recording Digital Pulse Processing (DPP) Tools

CAEN has developed a complete family of digitizers that consists of several models differing in sampling frequency, resolution, number of channels, form factor, memory size and other parameters.

The following table lists all models currently available. In parallel with the hardware development, CAEN has made a big effort in developing algorithms for the Digital Pulse Processing (DPP); the user can install a DPP algorithm on the FPGA of the digitizer (firmware upgrade), run

it on-line and implement new acquisition methods that go beyond the simple waveform recording. A digitizer with DPP becomes a new instrument that represents a fully digital replacement of most traditional modules such as Multi and Single-Channel Analyzers, QDCs, TDCs, Discriminators and many others.

| Мо                    | <b>iel</b> <sup>(1)</sup> | Form Factor | N. of ch. <sup>(2)</sup><br>Single-Ended | Max. Sampling<br>Frequency (MS/s) <sup>(2)</sup> | Resolution (bit) | Input Dynamic Range<br>(Vpp) <sup>(2)</sup> | Bandwidth (MHz) <sup>(2)</sup> | Memory (MS/ch) <sup>(2)</sup> | DPP firmware <sup>(3)</sup> |

|-----------------------|---------------------------|-------------|------------------------------------------|--------------------------------------------------|------------------|---------------------------------------------|--------------------------------|-------------------------------|-----------------------------|

| x7                    | 720                       | VME         | 8                                        | 250                                              | 12               | 2                                           | 125                            | 1.25 / 10                     | PSD                         |

|                       |                           | Desktop/NIM | 4/2                                      |                                                  |                  |                                             |                                |                               |                             |

|                       | VME                       | VME         | 8                                        | 100                                              | 14               | 0.5 / 2.25 / 10                             | 40                             | 0.5 / 4                       | PHA, DAW                    |

| X                     | 724                       | Desktop/NIM | 4/2                                      | 100                                              | 14               |                                             | 40                             |                               |                             |

| x                     | 725                       | VME         | 16/8                                     | 250                                              | 14               | 0.5 - 2                                     | 125                            | 0.64 / 5.12                   | PHA, PSD,                   |

| NEW                   | EW                        | Desktop/NIM | 8                                        | 250                                              |                  |                                             |                                |                               | ZLEplus COMING SOON         |

|                       | 730                       | VME         | 16/8                                     | 500                                              | 14               | 0.5 - 2                                     | 250                            | 0.64 / 5.12                   | PHA, PSD,                   |

|                       |                           | Desktop/NIM | 8                                        |                                                  |                  |                                             |                                |                               | ZLEplus COMING SOON         |

| x7                    | 740 VME<br>Desktop/NIM    | VME         | 64                                       | 62.5                                             | 12               | 2/10                                        | 30                             | 0.19/1.5                      | QDC                         |

|                       |                           | Desktop/NIM | 32                                       |                                                  | 12               | 2710                                        | 30                             | 0.1971.5                      | QDC                         |

|                       | VME 8                     | 8 - 4       | 1000 0000                                | 10                                               | -                | 500                                         | 1.8 - 3.6 / 14.4 -             | DOD 71 Entra                  |                             |

| X                     | 751                       | Desktop/NIM | 4 - 2                                    | 1000 - 2000                                      | 10               | 1                                           | 500                            | 28.8                          | PSD, ZLEplus                |

|                       | (761                      | VME         | 2                                        | 4000                                             | 10               | 1                                           | 1000                           | 7.2 / 57.6                    |                             |

| X                     |                           | Desktop/NIM | 1                                        | 4000                                             | 10               |                                             | 1000                           | 1.2/ 51.0                     | n.a.                        |

| HED                   | x742                      | VME         | 32+2                                     | E000 (4)                                         | 5000 (4) 12      | -                                           | 500                            | 0.100 / 1                     |                             |

|                       |                           | Desktop/NIM | 16+1                                     | 5000 \%                                          | 12               | 1                                           | 500                            | 0.128/1                       | n.a.                        |

| SWITCHED<br>CAPACITOR | x743                      | VME         | 16                                       | 2000 (4)                                         | 10               | 0.5                                         | 500                            | 0.007                         |                             |

|                       | x743                      | Desktop/NIM | 8                                        | 3200 (4)                                         | 12               | 2.5                                         | 500                            | 0.007                         | n.a.                        |

(1) The x in the model name is V1 for VME, VX1 for VME64X, DT5 for Desktop and N6 for NIM

(4) Sampling frequency of the analog memory (switched capacitor array); A/D conversion takes place at lower speed (thus generating a Dead Time.)

(2) The indication "size 1/ size 2" denotes different model versions while "size 1 - size 2" denotes different model operating modes

(3) Digital Pulse Processing (DPP) firmware:

• DPP-PHA: Pulse Height analysis (Trapezoidal Filter);

· DPP-PSD: Pulse Shape Discrimination;

DPP-ZLEplus: Digital Pulse Processing for the Zero Length Encoding (enhanced Zero Suppression algorithm):

DPP-DAW: Digital Pulse Processing for Dynamic Acquisition Window

DPP-QDC: Digital Pulse Processing for Charge to Digital Converter

Note: DPP-Cl is no longer supported. To perform Charge Integration, please refer to the DPP-PSD.

## **Principle of Operation**

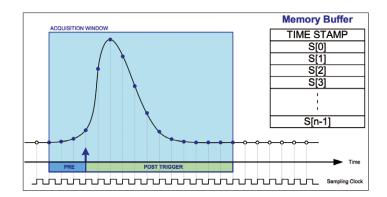

CAEN Digitizer shares with a digital oscilloscope essentially the basic operating, where the analogue signal is sampled by a flash ADC, whose output, i.e. the stream of digital samples, is continuously read by an FPGA and stored in a circular memory buffer of a programmable size. At the arrival of the trigger, the buffer is frozen and made available for the readout, while the acquisition can continue in a new buffer.

However, there are few important differences between a digitizer and a commercial digital oscilloscope:

- · On-line digital pulse processing (DPP) and data reduction

- Dead-timeless waveform recording

- · Independent channel self-triggering and event acquisition

- · Multi-board synchronization for system scalability

- · High bandwidth data readout links

The benefits of the digital approach are great stability and reproducibility, ability to reprogram and tailor the algorithms to the application, ability to preserve the information of the signal along the entire acquisition chain, flexibility, better correction of baseline fluctuation, pile-up, ballistic deficit, etc.. All in one board.

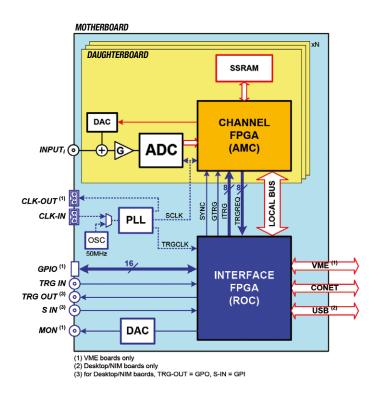

## CAEN Digitizer block diagram:

- The motherboard defines the form-factor; it contains one FPGA for the readout interfaces and the services

- The daughterboard defines the type of digitizer; it contains the signal conditioning input stage, the ADCs, the FPGA for the data processing and the memories

## 1. Digitizers allow for dead-timeless acquisition.

The digitizers have the ability to accept two consecutive triggers very close to each other thanks to the multi-buffer memory management: there is no dead time between an acquisition window and the next one. It is even possible to accept two triggers for which the acquisition windows overlap.

Dead-timeless feature is not supported by all digitizer models and all the firmware.

## 2. High flexibility of trigger configuration

Each channel of the digitizer is able to implement a digital discriminator that generates a trigger when a certain condition is met; in the basic implementation, this is just a programmable threshold which is continuously compared to the digitized input. More advanced algorithms (digital CFD, timing filters, etc.) are implemented in special DPP firmware. The individual channel self-trigger can be used to generate a global trigger for a simultaneous acquisition of all the channels within a board, can be propagated to the front panel connectors in order to make a multi-board triggering logic or can be used locally for an independent acquisition channel by channel (DPP mode only). It is also possible to combine the individual self-triggers to create a configurable coincidence or anticoincidence logic, either within the board or across multiple digitizers.

## 3. Scalability and synchronization of multi-board systems

In most cases, the applications that require the use of several channels need to synchronize the acquisition across different digitizers. This is performed according to the following points:

Distribution of a common clock reference in order to have the same sampling clock on all the ADC channels. CAEN digitizers feature a programmable PLL able to generate the sampling clocks locked to an external clock input, whose distribution can be done in parallel from a common source, using a fan-out, as well as through an in-out daisy chain with the ability to use the first board as a clock master (VME models only).

Alignment of the time stamp associated with the triggers to allow off-line reconstruction of the events read from different boards. This can be done by using an external signal as well as through an in-out daisy chain.

Distribution of the triggers from channel to channel and from board to board, according to a certain trigger logic. Each card has different trigger sources: external TRG-IN from the front panel, software trigger and channel self-triggers. All these triggers can be combined in order to make coincidences, majorities, global triggers and other functions.

## 4. High bandwidth data readout links

The digitizers are designed to provide high rate data transfer to a computer or an external data processing unit. CAEN digitizers have a bandwidth of  $\approx$ 30MB/s in the case of the USB, about 80MB/s with CONET port up to more than 120MB/s for the VME with 2eSST.

The communication interfaces allow the user to operate postprocessing data analysis.

## 5. Signal Digitization and Pulse Processing

The flash ADC technology has improved significantly in the last decades providing always higher resolution and faster sampling speed. The use of flash ADCs in acquisition boards gives the possibility to convert the analog signal preserving the information required by the experimental activities and the applications of nuclear techniques.

Digital acquisition devices described in this section represent multichannel waveform digitizers providing time information and digitized signal waveforms through fast communication interfaces, allowing the user to operate post-processing data analysis.

The waveform digitizers integrate also field programmable gate arrays (FPGA) which are able to acquire the information from flash ADC in real time and process it. Algorithms can be programmed, and their parameters can be adjusted to different experimental conditions. Those algorithms may be the digital replacement of the traditional analog signal processing, so that the waveform digitizer embeds different functions in one single board. In particular, it is possible to replace timing filters such as Constant Fraction Discriminators, shaper amplifier, Peak Sensing ADC, QDC, TDC, etc.

Most of the algorithms are implemented at firmware level inside the FPGA, which also manages the overall acquisition and data transfer. Data is read by a software, which is able to both program the digitizer and to perform the acquisition. Most advanced software also provides specific analysis tool, such as peak fitting.

## Acquisition Modes

CAEN Digitizers can be operated in different acquisition modes which are introduced in the next sections:

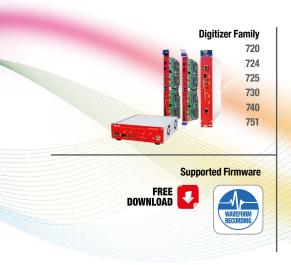

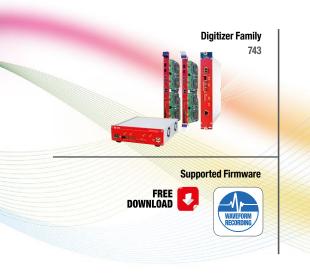

## 1. Waveform Recording

The digitizer is able to acquire, digitalize and record the input pulse within a programmable time window. Simplified zero suppression functions can be configured. All CAEN digitizers are equipped with their proper default firmware for waveform recording.

CAENScope and WaveDump software are available to manage the acquisition. Data can be saved in real time for offline analysis.

Furthermore, the 742 and 743 families, which come with two different switched capacitor chips, are well suitable for high precision time measurement of fast signals. WaveDump and the dedicated WaveCatcher software (free download) can control the acquisition of the two boards respectively.

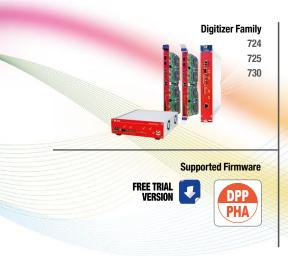

## 2. Digital Pulse Processing (DPP)

Where the algorithm inside the FPGA not only acquires the waveform, but also performs additional processing to get a set of significant information like energy, pulse shape and precise timing.

Pulse Height Analysis for gamma ray spectroscopy applies to voltage signals coming from HPGe/Si detectors and Scintillators coupled with Charge Sensitive Preamplifiers.

Works with independent channels event acquisition and in time stamped list mode.

Energy spectra are built by the supported software like the new CoMPASS and MC<sup>2</sup>Analyzer.

Pulse Shape Discrimination for gated charge integration<sup>(1)</sup> and gamma-neutron discrimination is suited for current signals coming from Scintillators, Gas tubes, SiPM and PMT. Works with independent channels event acquisition and in energy &

timing list mode. Features digital CFD and timing interpolation for high resolution time

information, as well as pulse shape discrimination. Energy spectra are built by the supported software like the new

CoMPASS and the DPP-PSD Control Software.

(1) DPP-Cl is no longer supported. To perform Charge Integration, please refer to the DPP-PSD.

| DPP    |  |

|--------|--|

|        |  |

| $\sim$ |  |

Charge to Digital Conversion implements a Gated Integrator receiving signals directly from the detector (no charge preamp required).

Suited for Scintillators and Gas detectors with medium-slow decay time, but can also work with faster detectors such as LaBr<sub>3</sub>. Designed for high channel density digitizers, can be used for multi-

channel acquisition in Detector Array systems. Features independent channel acquisition with self-gating capability for the charge integration (no additional delay lines, no external discriminator).

Energy and time stamped list mode provides timing information as well as energy information for spectra calculation.

Zero Length Encoding for advanced zero suppression works with a common trigger and simultaneous acquisition on all channels. The digitized waveforms are transferred in compressed mode by suppressing baseline and empty channels.

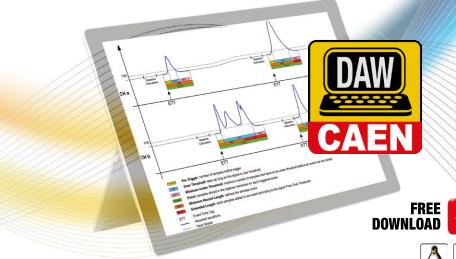

Dynamic Acquisition Window is suited for zero suppression with trigger-less acquisition systems.

Works in waveform mode and independent channels event acquisition dynamically stretching the acquisition window (record length) to fit the actual input pulse duration.

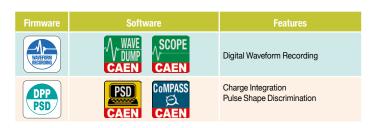

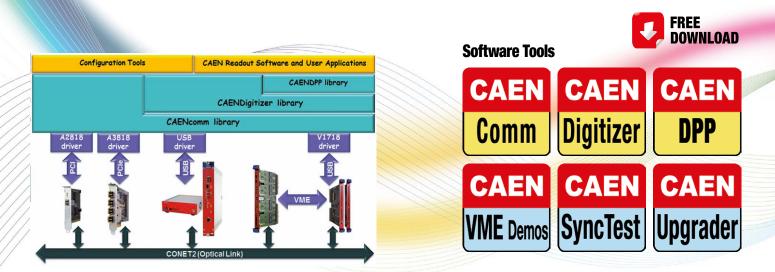

## **Software Tools**

CAEN provides drivers to integrate its boards in the host PC system, libraries and Demos for software custom development, and configuration software utilities.

Depending on the final purpose, the user can select the best fitting hardware and firmware solution with the supported CAEN software, as reported in the following table.

| Туре      | Aquisition Mode          | Features                                                                                                         | Firmware <sup>(1)</sup> | Software <sup>(2)</sup>          | Family                                             |

|-----------|--------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------|----------------------------------------------------|

|           |                          | Gated Charge Integration<br>Pulse Shape Discimination                                                            | DPP<br>PSD              | COMPASS<br>CAEN CAEN             | x720 <sup>(3)</sup>                                |

|           | 5                        | Gated Charge Integration<br>Pulse Shape Discrimination<br>Constant Fraction Discriminator & Timing Interpolation | DPP<br>PSD              | PSD Compass 英<br>Caen Caen       | x725<br>x730<br>x751                               |

|           | e Processin              | Digital QDC<br>Charge Integration                                                                                | DPP                     | Compass<br>Caen Caen             | x740 <sup>(6)</sup>                                |

|           | Digital Pulse Processing | Pulse Height Analysis                                                                                            | DPP<br>PHA              |                                  | x724 <sup>(4)</sup><br>x725<br>x730                |

|           |                          | Digital Waveform Recorder with Enhanced Zero Surpression                                                         | DPP                     | ZLE <sup>1</sup><br>CAEN         | x725 <sup>(5)</sup><br>x730 <sup>(5)</sup><br>x751 |

| Digitizer |                          | Digital Waveform Recorder with Zero Suppression for trigger-less acquisition systems                             | DPP                     | DAW.<br>CAEN                     | x724                                               |

|           |                          | Digital Waveform Recorder                                                                                        | WEEKERM                 |                                  | x742                                               |

|           |                          |                                                                                                                  |                         | V DUMP<br>CAEN                   | x761                                               |

|           |                          |                                                                                                                  |                         |                                  | x720                                               |

|           | ordinç                   |                                                                                                                  |                         |                                  | x724                                               |

|           | n Reci                   |                                                                                                                  |                         | √ <u>WAVE</u> <sub>∧</sub> SCOPE | x725                                               |

|           | veforn                   |                                                                                                                  |                         | CAEN CAEN                        | x730<br>x740                                       |

|           | War                      |                                                                                                                  |                         |                                  | x740<br>x751                                       |

|           |                          | Digital Waveform Recorder<br>Charge Integration<br>Constant Fraction Discrimination                              | WEEGOM                  |                                  | x743                                               |

(1) DPP firmware: free trial version

Waveform Recording firmware (Default): free download

(2) Free Download

(3) DPP-CI firmware and DPP-CI Control Software are no longer supported. To perform Charge Integration please refer to the DPP-PSD firmware and software

(4) DPP-PHA, starting from rev. 128.64 of the AMC FPGA firmware, is no longer supported by x724 models equipped with EP1C4 Altera FPGA

(5) DPP-ZLE Plus for x725 and x730 families: Coming Soon

(6) CoMPASS software for DPP-QDC: Coming Soon DPP-QDC firmware runs only on x740D digitizer models

## **Application Notes**

CAEN provides a wide selection of application notes, white papers and scientific articles focused on digitizers and their use in different fields. In these documents, the capability and flexibility of CAEN digitizers are well exploited showing their physics-driven development.

Here follows a brief selection:

- AN2086 Synchronization of CAEN Digitizers in Multiple Board Acquisition Systems

- AN2503 Charge Integration: Analog Vs. Digital

- AN2506 Digital Gamma Neutron discrimination with Liquid Scintillators

AN2508 CAEN Digital Pulse Height Analyser a digital approach to Radiation Spectroscopy

- AN2770 Digital ToF Measurements of Fast Neutrons in a Spallation Neutron Source

- WP2081 Digital Pulse Processing in Nuclear Physics

- AR2614 Tests of PMT Signal Read-out in a Liquid Argon Dark Matter Detector with a New Fast Waveform Digitizer

- AR2613 Special nuclear material detection with a mobile multidetector system

- AR2612 First demonstration of a Compton gamma imager based on silicon photomultipliers

- AR2593 Diamond detectors for fast neutron measurements at pulsed spallation sources

- GD2827 How to make coincidences with CAEN digitizers

- AN3250 Pulse Shape Discrimination with different CAEN digitizers running DPP-PSD firmware

- AN3251 Time Measurements with CAEN Waveform Digitizers

All these documents are available for download in the Document Library section of CAEN website.

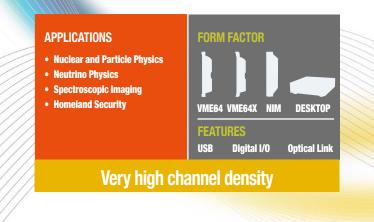

## APPLICATIONS

- Nuclear and Particle PhysicsDark Matter and Astroparticle

- PhysicsFast Neutron spectroscopy,

- Fusion Plasma diagnostics

Environmental monitoring, Homeland Security

## A cost- effective, general purpose choice

# 720 Digitizer Family 8/4/2 Ch. 12-bit 250 MS/s Digitizer

## **Overview**

The 720 is a family of 12-bit and 250 MS/s Flash ADC Waveform Digitizers with 2 Vpp of input dynamic range and DC offset adjustment.

It is available in three form factors: VME (8 input channels), NIM (4 or 2 input channels) and Desktop (4 or 2 input channels).

Considering the sampling frequency and the bit number, these digitizers are well suited for mid-fast signals as the ones coming from liquid or inorganic scintillators coupled to PMTs or Silicon Photomultipliers.

The acquisition capabilities take advantage of the multi-buffer organization of the channel memory (divisible into a maximum of 1024 buffers). The data stream is continuously written in a circular memory buffer. When the trigger occurs, the digitizer writes further samples for the post trigger and freezes the buffer that can be read by one of the provided readout links. The acquisition can continue without any dead time in a new buffer. Two memory sizes are available according to the different versions of the x720 model: 1.25 MS/ch or 10 MS/ch.

The on-board FPGAs can run default firmware for waveform recording (including 'Zero suppression' and 'data reduction' methods that allow substantial savings in data amount readout and processing) as well as Digital Pulse Processing algorithms (DPP) making the digitizer an enhanced system for Physics applications. In addition to the existing firmware selection, CAEN is willing to collaborate with customers for developing custom solutions.

A common acquisition trigger signal can be provided externally, via front panel digital input connector, or via software. Alternatively, each channel can generate a trigger request when the input pulse goes under/over a programmable threshold; the trigger requests can be used either locally by the channel (independent triggering with DPP firmware) or processed by the board to generate a common trigger causing all the enable channels to acquire an event simultaneously

(default firmware). The trigger from one board can be provided out on a front panel digital output connector.

720 family supports multi-board synchronization making a multi-board system where all ADCs result to be synchronized to a common clock source, and ensuring Trigger Time Tag alignment. Once synchronized, all data will be aligned and coherent across multiple x720 boards.

## **Features**

0

0

0

0

0

0.0

- 12-bit @ 250 MS/s

- · Analog inputs on MCX coax. connectors (single ended)

- VME64/VME64X (8 ch.), NIM (4 or 2 ch.) and Desktop (4 or 2 ch.) modules

- 2 Vpp input dynamic range with programmable DC offset adjustment

- Algorithms for Digital Pulse Processing (DPP)

- · VME, USB and Optical Link communication interfaces

- Multi-board synchronization features

- · Daisy chain capability

- Demo software tools, Control Software for default and DPP firmware, C and LabVIEW libraries

## **Technical Specifications**

## GENERAL

Form Factor 1-unit wide, 6U VME64/VME64X 1-unit wide NIM 154x50x164 mm3 (WxHxD) Desktop

## **ANALOG INPUT**

Channels 8 channels, single ended (VME) 4/2 channels, single ended (NIM, Desktop) Impedance 50 0 Connector MCX Full Scale Range (FSR) 2 Vpp Bandwidth 125 MHz Offset Programmable DAC for DC offset adjustment. Range: ±1 V

#### **DIGITAL CONVERSION**

Resolution 12 bits Sampling rate 31.25 to 250 MS/s simultaneously on each channel

#### ADC CLOCK GENERATION

Clock source: internal/external

On-Board PLL provides ADC sampling clock generation from an internal (50 MHz loc. oscillator) or external (front panel CLK-IN connector) reference

#### MEMORY

1.25 MS/ch or 10 MS/ch Multi Event Buffer with independent read and write access divisible into 1 ÷ 1024 buffers

Programmable event size and pre-post trigger

#### TRIGGER

**Trigger sources**

Self-trigger: channel over/under threshold for either Common or Individual (DPP firmware only) trigger generation

External-trigger: Common by TRG-IN or Individual by LVDS connectors (DPP firmware only) Software-trigger: Common by software command

Trigger propagation TRG-OUT (VME) / GPO (NIM and Desktop) digital output

Trigger Time Stamp Default firmware: 31-bit counter, 16 ns resolution, 17 s range(\*); 48-bit extension by firmware DPP-CI/PSD Firmware: 32-bit counter, 4 ns resolution, 17 s range; 64-bit extension by software

#### **SYNCHRONIZATION**

Clock propagation Daisy chain (VME only) by CLK-IN/CLK-OUT connectors One-to-many clock distribution from an external clock source Clock Cable delay compensation Acquisition Synchronization Sync Start/Stop by digital I/O (S-IN, TRG-IN or GPI input, TRG-OUT or GPO output) External Trigger Time Stamp reset

#### LVDS I/O (VME only)

16 general purpose LVDS I/Os controlled by FPGA Busy, Data Ready, Memory full, Individual Trig-Out and other functions can be programmed An Input Pattern from the LVDS I/Os can be associated to each trigger as an event marker

#### ANALOG MONITOR (VME only)

12-bit/100 MHz DAC FPGA controlled output with four operating modes: Trigger Majority / Test Pulses / Memory Occupancy / Voltage Level

#### **COMMUNICATION INTERFACE**

Ontical Link CAEN CONET proprietary protocol, up to 80 MB/s transfer rate Daisy chainable: it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod. A2818/A3818) USB (NIM and Desktop direct, VME via V1718 bridge) USB 2.0 compliant Transfer rate up to 30 MB/s VMF

VME 64X compliant Data transfer mode: BLT32, MBLT64 (70 MB/s using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s)

(\*) Trigger Logic and Trigger Time Stamp counter operate at 125 MHz (i.e. 8 ns or 1/2 ADC clock cycles), while the counter value is read at a frequency of 62.5 MHz (i.e. 16 ns).

## **POWER CONSUMPTIONS**

Desktop: 1.5 A @ 12 V (Typ.) NIM: 2.9 A @ +6 V, 90 mA @ -6 V VME: 4 A @ +5 V, 200 mA @ +12 V, 200 mA @ -12 V

| Code         | Description                                                              | Form Factor |

|--------------|--------------------------------------------------------------------------|-------------|

| WDT5720BXAAA | DT5720B - 4 Ch. 12 bit 250 MS/s Digitizer: 1.25MS/ch, C20, SE            | Desktop     |

| WDT5720CXAAA | DT5720C - 2 Ch. 12 bit 250 MS/s Digitizer: 1.25MS/ch, C20, SE            | Desktop     |

| WDT5720DXAAA | DT5720D - 4 Ch. 12 bit 250 MS/s Digitizer: 10MS/ch, C20, SE              | Desktop     |

| WDT5720EXAAA | DT5720E - 2 Ch. 12 bit 250 MS/s Digitizer: 10MS/ch, C20, SE              | Desktop     |

| WN6720BXAAAA | N6720B - 4 Ch. 12 bit 250 MS/s Digitizer: 1.25MS/ch, C20, SE             | NIM         |

| WN6720CXAAAA | N6720C - 2 Ch. 12 bit 250 MS/s Digitizer: 1.25MS/ch, C20, SE             | NIM         |

| WN6720DXAAAA | N6720D - 4 Ch. 12 bit 250 MS/s Digitizer: 10MS/ch, C20, SE               | NIM         |

| WN6720EXAAAA | N6720E - 2 Ch. 12 bit 250 MS/s Digitizer: 10MS/ch, C20, SE               | NIM         |

| WV1720EXAAAA | V1720E - 8 Ch. 12 bit 250 MS/s Digitizer: 1.25MS/ch, C20, SE             | 6U-VME64    |

| WV1720GXAAAA | V1720G - 8 Ch. 12 bit 250 MS/s Digitizer: 10MS/ch, C20, SE               | 6U-VME64    |

| WVX1720EXAAA | VX1720E - 8 Ch. 12 bit 250 MS/s Digitizer: 1.25MS/ch, C20, SE            | 6U-VME64X   |

| WVX1720GXAAA | VX1720G - 8 Ch. 12 bit 250 MS/s Digitizer: 10MS /ch, C20, SE             | 6U-VME64X   |

| WFWDPPNGAA20 | DPP-PSD - Digital Pulse Processing for Pulse Shape Discrimination (x720) | ALL         |

## Accessories

A2818 PCI CONET Controller

A654 MCX to LEMO Cable Adapter 91

A317 MCX to BNC Cable Adapter

**Clock Distribution Cable**

A659

Cables for CONET Optical Link Networks

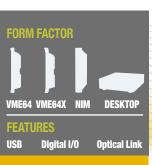

FORM FACTOR

VME64 VME64X NIM

Digital I/O

DESKTOP

**Optical Link**

0

$\overline{\mathbf{o}}$

0

0

Õ

0.8

## APPLICATIONS

- Nuclear and Particle Physics

- X-ray and Gamma Spectroscopy with HPGe, Silicon detectors

Spectroscopic Imaging for

- Homeland Security

Segmented detectors, Medical Imaging, Material science

USB

# 724 Digitizer Family 8/4/2 Ch. 14-bit 100 MS/s Digitizer

## **Overview**

The 724 is a family of 14-bit and 100 MS/s Flash ADC Waveform Digitizers with 2.25 Vpp of input dynamics (optionally 0.5 or 10 Vpp) and DC offset adjustment.

It is available in three form factors: VME (8 input channels), NIM (4 or 2 input channels) and Desktop (4 or 2 input channels).

Considering the sampling frequency and the bit number, these digitizers are well suited for high resolution detectors as Silicon, HPGe coupled to Charge Sensitive Preamplifiers or inorganic scintillators like Nal or Csl.

The acquisition capabilities take advantage of the multi-buffer organization of the channel memory (divisible into a maximum of 1024 buffers). The data stream is continuously written in a circular memory buffer. When the trigger occurs, the digitizer writes further samples for the post trigger and freezes the buffer that can be read by one of the provided readout links. The acquisition can continue without any dead time in a new buffer. Two memory sizes are available according to the different versions of the x724 model: 512 kS/ch or 4 MS/ch.

The on-board FPGAs can run default firmware for waveform recording (including 'Zero suppression' and 'data reduction' methods that allow substantial savings in data amount readout and processing) as well as Digital Pulse Processing algorithms (DPP) making the digitizer an enhanced system for Physics applications. In addition to the existing firmware selection, CAEN is willing to collaborate with customers for developing custom solutions.

A common acquisition trigger signal can be provided externally, via front panel digital input connector, or via software. Alternatively, each channel can generate a trigger request when the input pulse goes

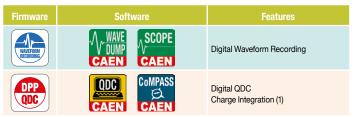

| Firmware                 | Software                                  | Features                                                                                    |

|--------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|

| WAVEFORM                 | A WAVE SCOPE                              | Digital Waveform Recording                                                                  |

| <b>DPP</b><br><b>PHA</b> | MC <sup>2</sup> Compass<br>ズ<br>CAEN CAEN | Pulse Height Analysis                                                                       |

| DPP                      |                                           | Digital Waveform Recording with Zero<br>Suppression for trigger-less acquisition<br>systems |

under/over a programmable threshold; the trigger requests can be used either locally by the channel (independent triggering with DPP firmware) or processed by the board to generate a common trigger causing all the enable channels to acquire an event simultaneously (default firmware). The trigger from one board can be provided on a front panel digital output connector.

724 family supports multi-board synchronization making a multi-board system where all ADCs result to be synchronized to a common clock source, and ensuring Trigger Time Tag alignment. Once synchronized, all data will be aligned and coherent across multiple x724 boards.

## Features

#### • 14-bit @ 100 MS/s

- · Analog inputs on MCX coax. connectors (single ended)

- VME64/VME64X (8 ch.), NIM (4 or 2 ch.) and Desktop (4 or 2 ch.) modules

- 0.5, 2.25 or 10 Vpp input dynamic range with programmable DC offset adjustment

- · Algorithms for Digital Pulse Processing (DPP)

- · VME, USB and Optical Link communication interfaces

- Multi-board synchronization features

- · Daisy chain capability

- Demo software tools, Control Software for default and DPP firmware, C and LabVIEW libraries

## **Technical Specifications**

## GENERAL

Form Factor 1-unit wide, 6U VME64/VME64X 1-unit wide NIM 154x50x164 mm3 (WxHxD) Desktop

## ANALOG INPUT

Channels 8 channels, single ended (VME) 4/2 channels, single ended (NIM, Desktop) Impedance 50  $\Omega$  (2.25 and 0.5 Vpp), 1 k  $\Omega$  (10 Vpp) Connector MCX Full Scale Range (FSR) 2.25 Vpp (0.5 or 10 Vpp by ordering code) Bandwidth 40 MHz Offset Programmable DAC for DC offset adjustment. Range: ±1.125 @ 2.25 Vpp, ±0.25 @ 0.5 Vpp, ±5 V @ 10 Vpp

#### **DIGITAL CONVERSION**

Resolution 14 bits Sampling rate 32.2 to 100 MS/s simultaneously on each channel

#### ADC CLOCK GENERATION

Clock source: internal/external

On-Board PLL provides ADC sampling clock generation from an internal (50 MHz loc. oscillator) or external (front panel CLK-IN connector) reference

#### MEMORY

512 KS/ch or 4 MS/ch Multi-Event Buffer with independent read and write access divisible into

1 ÷ 1024 buffers. Programmable event size and pre-post trigger

#### TRIGGER

**Trigger sources**

Self-trigger: channel over/under threshold for either Common or Individual (DPP firmware only) trigger generation

External-trigger: Common by TRG-IN or Individual by LVDS connectors (DPP firmware only) Software-trigger: Common by software command

Trigger propagation

TRG-OUT (VME) / GPO (NIM and Desktop) digital output **Trigger Time Stamp**

Default firmware: 31-bit counter, 20 ns resolution, 21 s range(\*); 48-bit extension by firmware DPP-PHA Firmware: 30-bit counter, 10 ns resolution, 10 s range; 64-bit extension by software DPP-DAW Firmware: 31-bit counter, 10 ns resolution, 21 s range; 64-bit extension by software

#### **SYNCHRONIZATION**

**Clock propagation**

Daisy chain (VME only) through CLK-IN/CLK-OUT connectors One-to-many clock distribution from an external clock source Clock Cable delay compensation Acquisition Synchronization Acquisition Synchronization

Sync Start/Stop through digital I/O (S-IN, TRG-IN or GPI input, TRG-OUT or GPO output) External Trigger Time Stamp reset

#### LVDS I/O (VME only)

16 general purpose LVDS I/Os controlled by FPGA Busy, Data Ready, Memory full, Individual Trig-Out and other functions can be programmed An Input Pattern from the LVDS I/Os can be associated to each trigger as an event marker

#### ANALOG MONITOR (VME only)

12-bit/100 MHz DAC FPGA controlled output with four operating modes: Trigger Majority / Test Pulses / Memory Occupancy / Voltage Level

#### **COMMUNICATION INTERFACE**

**Optical Link** CAEN CONET proprietary protocol, up to 80 MB/s transfer rate Daisy chainable: it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod. A2818/A3818) USB (NIM and Desktop direct, VME via V1718 bridge) USB 2.0 compliant Transfer rate up to 30 MB/s VMF

#### VME 64X compliant

Data transfer mode: BLT32, MBLT64 (70 MB/s using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s)

## POWER CONSUMPTIONS

Desktop: 1.7 A @ 12 V (Typ.) NIM: 3.9 A @ +6 V, 90 mA @ -6 V VME: 4.5 A @ +5 V, 200 mA @ +12 V, 200 mA @ -12 V

(\*) Trigger Logic and Trigger Time Stamp counter operate at 100 MHz (i.e. 10 ns or 1 ADC clock cycle), while the counter value is read at a frequency of 50 MHz (i.e. 20 ns).

| Ordering | Options |

|----------|---------|

|----------|---------|

| Code         | Description                                                               | Form Factor |

|--------------|---------------------------------------------------------------------------|-------------|

| WDT5724BXAAA | DT5724B - 4 Ch. 14 bit 100 MS/s Digitizer: 512kS/ch, C20, SE              | Desktop     |

| WDT5724CXAAA | DT5724C - 2 Ch. 14 bit 100 MS/s Digitizer: 512kS/ch, C20, SE              | Desktop     |

| WDT5724FXAAA | DT5724F - 4 Ch. 14 bit 100 MS/s Digitizer: 4MS/ch, C20, SE                | Desktop     |

| WDT5724GXAAA | DT5724G - 2 Ch. 14 bit 100 MS/s Digitizer: 4MS/ch, C20, SE                | Desktop     |

| WN6724BXAAAA | N6724B - 4 Ch. 14 bit 100 MS/s Digitizer: 512kS/ch,C20, SE                | NIM         |

| WN6724CXAAAA | N6724C - 2 Ch. 14 bit 100 MS/s Digitizer: 512kS/ch, C20, SE               | NIM         |

| WN6724FXAAAA | N6724F - 4 Ch. 14 bit 100 MS/s Digitizer: 4MS/ch,C20, SE                  | NIM         |

| WN6724GXAAAA | N6724G - 2 Ch. 14 bit 100 MS/s Digitizer: 4MS/ch, C20, SE                 | NIM         |

| WV1724EXAAAA | V1724E - 8 Ch. 14 bit 100 MS/s Digitizer: 4MS/ch, C20, SE                 | 6U-VME64    |

| WV1724GXAAAA | V1724G - 8 Ch. 14 bit 100 MS/s Digitizer: 512KS/ch, C20, SE               | 6U-VME64    |

| WVX1724EXAAA | VX1724E - 8 Ch. 14 bit 100 MS/s Digitizer: 4MS/ch, C20, SE                | 6U-VME64X   |

| WPERS0172401 | 724 Customization - 10Vpp Input Range, SE                                 | ALL         |

| WPERS0172402 | 724 Customization - 500mVpp Input Range, SE                               | ALL         |

| WFWDPPTFAAAA | DPP-PHA - Digital Pulse Processing for Pulse Height Analysis (x724)       | ALL         |

| WFWDPPDAWXEA | DPP-DAW - Digital Pulse Processing with Dynamic Acquisition Window (x724) | ALL         |

**Accessories**

4654 MCX to LEMO Cable Adapter 93

A659 MCX to BNC Cable Adapter A317 Clock Distribution Cable

A318 SE to Differential Clock Cable

Adapter

AI2700 **Optical Fiber Series**

Cables for CONET Optical Link Networks

## **APPLICATIONS**

- Nuclear and Particle Physics

Dark Matter and Astroparticle

Physics

- Fast Neutron spectroscopy

- Homeland Security

## **Maximum flexibility**

# **NEW** 725 Digitizer Family 16/8 Ch. 14-bit 250 MS/s Digitizer

## **Overview**

The 725 is a family of 14-bit and 250 MS/s Flash ADC Waveform Digitizers with software selectable 0.5 Vpp or 2 Vpp (default) input dynamic range and DC offset adjustment.

It is available in three form factors: VME (16/8 input channels), NIM (8 input channels) and Desktop (8 input channels).

Considering the sampling frequency and the bit number, these digitizers are well suited for mid-fast signals as the ones coming from liquid or inorganic scintillators coupled to PMTs or Silicon Photomultipliers, and others.

The acquisition capabilities take advantage of the multi-buffer organization of the channel memory (divisible into a maximum of 1024 buffers). The data stream is continuously written in a circular memory buffer. When the trigger occurs, the digitizer writes further samples for the post trigger and freezes the buffer that can be read by one of the provided readout links. The acquisition can continue without any dead time in a new buffer. Two memory sizes are available according to the different versions of the x725 model: 640 kS/ch or 5.12 MS/ch.

The on-board FPGAs can run default firmware for waveform recording as well as Digital Pulse Processing algorithms (DPP) making the digitizer an enhanced system for Physics applications. In addition to the existing firmware selection, CAEN is willing to collaborate with customers for developing custom solutions.

A common acquisition trigger signal can be provided externally, via front panel digital input connector, or via software. Alternatively, each

| Firmware                 | Software                                  | Features                                                                            |

|--------------------------|-------------------------------------------|-------------------------------------------------------------------------------------|

| WAVEFORM                 |                                           | Digital Waveform Recording                                                          |

| DPP<br>PSD               | CAEN Compass                              | Charge Integration<br>Pulse Shape Discrimination<br>Constant Fraction Discriminator |

| <b>DPP</b><br><b>PHA</b> | MC <sup>2</sup> Compass<br>ズ<br>CAEN CAEN | Pulse Height Analysis                                                               |

| DPP                      |                                           | Digital Waveform Recording with<br>Enhanced Zero Suppression                        |

channel can generate a trigger request when the input pulse goes under/over a programmable threshold; the trigger requests can be used either locally by the channel (independent triggering with DPP firmware) or processed by the board to generate a common trigger causing all the enable channels to acquire an event simultaneously (default firmware). The trigger from one board can be provided on a front panel digital output connector.

725 family supports multi-board synchronization making a multi-board system where all ADCs result to be synchronized to a common clock source, and ensuring Trigger Time Tag alignment. Once synchronized, all data will be aligned and coherent across multiple x725 boards.

## **Features**

- 14-bit @ 250 MS/s

- · Analog inputs on MCX coax. connectors

- VME64/VME64X (16/8 ch.), NIM (8 ch.) and Desktop (8 ch.) modules

- 0.5 and 2 Vpp input dynamic range with programmable DC offset adjustment

- Algorithms for Digital Pulse Processing (DPP)

- VME, USB and Optical Link communication interfaces

- Multi-board synchronization features

- · Daisy chain capability

- Demo software tools, Control Software for default and DPP firmware, C and LabVIEW libraries

V1725x

TRD

## **Technical Specifications**

## GENERAL

Form Factor 1-unit wide. 6U VME64/VME64X 1-unit wide NIM 154x50x164 mm3 (WxHxD) Desktop

## ANALOG INPUT

Channels 16/8 channels, single ended (VME) 8 channels, single ended (NIM, Desktop) Impedance 50 Ω Connector MCX Full Scale Range (FSR) 0.5 or 2 Vpp (default) software selectable

#### Bandwidth 125 MHz

Offset

Programmable DAC for DC offset adjustment. Range: ±1 V @ 2 Vpp, ±0.25 V @ 0.5 Vpp

## **DIGITAL CONVERSION**

Resolution 14 bits Sampling rate 250 MS/s simultaneously on each channel

#### ADC CLOCK GENERATION Clock source: internal/external

On-Board PLL provides ADC sampling clock generation from an internal (50 MHz loc. oscillator) or external (front panel CLK-IN connector) reference

#### MEMORY

640 kS/ch or 5.12 MS/ch Multi-Event Buffer with independent read and write access divisible into 1 ÷ 1024 buffers. Programmable event size and pre-post trigger

## TRIGGER

**Trigger source**

Self-trigger: channel over/under threshold for either Common or Individual (DPP firmware only) trigger generation

External-trigger: Common by TRG-IN or Individual by LVDS connectors (DPP firmware only) Software-trigger: Common by software command

Trigger propagation

TRG-OUT (VME) / GPO (NIM, Desktop) digital output

**Trigger Time Stamp**

Default Firmware: 31-bit counter, 16 ns resolution, 17 s range(\*); 48-bit extension by firmware DPP-PHA/PSD: 31-bit counter, 4 ns resolution, 8 s range; 47-bit extension by firmware; 10-bit and 4 ps fine time stamp by digital CFD; 64-bit extension by software

#### **SYNCHRONIZATION**

**Clock propagation**

Daisy chain (VME only) through CLK-IN/CLK-OUT connectors One-to-many clock distribution from an external clock source

Clock Cable delay compensation

Acquisition Synchronization

Sync Start/Stop through digital I/O (S-IN, TRG-IN or GPI input, TRG-OUT or GPO output) External Trigger Time Stamp reset

#### LVDS I/O (VME only)

16 general purpose LVDS I/Os controlled by FPGA Busy, Data Ready, Memory Full, Individual Trg-Out and other functions can be programmed

An Input Pattern from the LVDS I/Os can be associated to each trigger as an event marker

#### ANALOG MONITOR (VME only)

12-bit/100 MHz DAC FPGA controlled output with four operating modes: Trigger Majority / Test Pulses / Memory Occupancy / Voltage Level

#### **COMMUNICATION INTERFACE**

**Optical Link** CAEN CONET proprietary protocol, up to 80 MB/s transfer rate Daisy chainable: it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod.A2818/A3818) VME VME 64X compliant

Data transfer mode: BLT32, MBLT64 (70 MB/s using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s)

**POWER CONSUMPTIONS**

#### Desktop: TBD NIM: TBD VME: V1725 5.2 A @ +5 V 750 mA @ +12 V

-12 V not used

#### **Ordering Options**

| Code         | Description                                                              | Form Factor |

|--------------|--------------------------------------------------------------------------|-------------|

| WDT5725XAAAA | DT5725 - 8 Ch. 14 bit 250 MS/s Digitizer: 640kS/ch, CE30, SE             | Desktop     |

| WDT5725BXAAA | DT5725B - 8 Ch. 14 bit 250 MS/s Digitizer: 5.12MS/ch, CE30, SE           | Desktop     |

| WN6725XAAAAA | N6725 - 8 Ch. 12/14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE           | NIM         |

| WN6725BXAAAA | N6725B - 8 Ch. 12/14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE         | NIM         |

| WV1725XAAAAA | V1725 - 16 Ch. 14 bit 250 MS/s Digitizer: 640kS/ch, CE30, SE             | 6U-VME64    |

| WV1725BXAAAA | V1725B - 16 Ch. 14 bit 250 MS/s Digitizer: 5.12MS/ch, CE30, SE           | 6U-VME64    |

| WV1725CXAAAA | V1725C - 8 Ch. 14 bit 250 MS/s Digitizer: 640kS/ch, CE30, SE             | 6U-VME64    |

| WV1725DXAAAA | V1725D - 8 Ch. 14 bit 250 MS/s Digitizer: 5.12MS/ch, CE30, SE            | 6U-VME64    |

| WVX1725XAAAA | VX1725 - 16 Ch. 14 bit 250 MS/s Digitizer: 640kS/ch, CE30, SE            | 6U-VME64X   |

| WVX1725BXAAA | VX1725B - 16 Ch. 14 bit 250 MS/s Digitizer: 5.12MSch, CE30, SE           | 6U-VME64X   |

| WVX1725CXAAA | VX1725C - 8 Ch. 14 bit 250 MS/s Digitizer: 640kS/c, CE30, SE             | 6U-VME64X   |

| WVX1725DXAAA | VX1725D - 8 Ch. 14 bit 250 MS/s Digitizer: 5.12MS/ch, CE30, SE           | 6U-VME64X   |

| WFWDPPTFAA25 | DPP-PHA - Digital Pulse Processing for Pulse Height Analysis (x725)      | ALL         |

| WFWDPPNGAA25 | DPP-PSD - Digital Pulse Processing for Pulse Shape Discrimination (x725) | ALL         |

#### **Accessories**

A2818 PCI CONET Controller

#### A3818 PCI Express CONET2 Controller

MCX to LEMO Cable Adapter

**Clock Distribution Cable**

A317

A654

95

A318 SE to Differential Clock Cable Adapter

MCX to BNC Cable Adapter

AI2700 **Optical Fiber Series**

A659

Cables for CONET Optical Link Networks

(\*) Trigger Logic and Trigger Time Stamp counter operate at 125 MHz (i.e. 8 ns or 2 ADC clock cycles), while the counter value is read at a frequency of 62.5 MHz (i.e. 16 ns).

## APPLICATIONS

- Nuclear and Particle Physics

Dark Matter and Astroparticle Physics

- Fast Neutron spectroscopy

- Homeland Security

Excellent resolution and fast sampling combined

# **730 Digitizer Family** 16/8 Ch. 14-bit 500 MS/s Digitizer

## **Overview**

The 730 is a family of 14-bit and 500 MS/s Flash ADC Waveform Digitizers with software selectable 0.5 Vpp or 2 Vpp (default) input dynamic range and DC offset adjustment.

It is available in three form factors: VME (16/8 input channels), NIM (8 input channels) and Desktop (8 input channels).

Considering the sampling frequency and the bit number, these digitizers are well suited for mid-fast signals as the ones coming from liquid or inorganic scintillators coupled to PMTs or Silicon Photomultipliers, and others.

The acquisition capabilities take advantage of the multi-buffer organization of the channel memory (divisible into a maximum of 1024 buffers). The data stream is continuously written in a circular memory buffer. When the trigger occurs, the digitizer writes further samples for the post trigger and freezes the buffer that can be read by one of the provided readout links. The acquisition can continue without any dead time in a new buffer. Two memory sizes are available according to the different versions of the x730 model: 640 kS/ch or 5.12 MS/ch.

The on-board FPGAs can run default firmware for waveform recording as well as Digital Pulse Processing algorithms (DPP) making the digitizer an enhanced system for Physics applications. In addition to the existing firmware selection, CAEN is willing to collaborate with customers for developing custom solutions.

A common acquisition trigger signal can be provided externally, via front panel digital input connector, or via software. Alternatively, each

| VAVE SCOPE Digital Waveform Recordi                                                                                   |      |

|-----------------------------------------------------------------------------------------------------------------------|------|

| CAEN CAEN                                                                                                             | ing  |

| Compass<br>Compass<br>Compass<br>Charge Integration<br>Pulse Shape Discrimination<br>Constant Fraction Discrimination |      |

| CAEN CoMPASS                                                                                                          |      |

| DIgital Waveform Record<br>Enhanced Zero Suppress                                                                     | sion |

0

0

0

6

0

D

channel can generate a trigger request when the input pulse goes under/over a programmable threshold; the trigger requests can be used either locally by the channel (independent triggering with DPP firmware) or processed by the board to generate a common trigger causing all the enable channels to acquire an event simultaneously (default firmware). The trigger from one board can be provided out on a front panel digital output connector.

730 family supports multi-board synchronization making a multi-board system where all ADCs result to be synchronized to a common clock source, and ensuring Trigger Time Tag alignment. Once synchronized, all data will be aligned and coherent across multiple x730 boards.

## **Features**

- 14-bit @ 500 MS/s

- · Analog inputs on MCX coax. connectors

- · VME64/VME64X (16/8 ch.), NIM (8 ch.) and Desktop (8 ch.) modules

- 0.5 and 2 Vpp input dynamic range with programmable DC offset adjustment

- · Algorithms for Digital Pulse Processing (DPP)

- VME, USB and Optical Link communication interfaces

- Multi-board synchronization features

- · Daisy chain capability

- Demo software tools, Control Software for default and DPP firmware, C and LabVIEW libraries

V1730B

## **Technical Specifications**

## GENERAL

Form Factor 1-unit wide, 6U VME64/VME64X 1-unit wide NIM 154x50x164 mm3 (WxHxD) Desktop

## ANALOG INPUT

Channels 16/8 channels, single ended (VME) 8 channels, single ended (NIM, Desktop) Impedance 50 0 Connector MCX Full Scale Range (FSR) 0.5 or 2 Vpp (default) software selectable

Randwidth 250 MHz

## Offset

Programmable DAC for DC offset adjustment. Range: ±1 V @ 2 Vpp, ±0.25 V @ 0.5 Vpp **DIGITAL CONVERSION**

#### Resolution

14 bits Sampling rate 500 MS/s simultaneously on each channel

#### ADC CLOCK GENERATION

Clock source: internal/external

On-Board PLL provides ADC sampling clock generation from an internal (50 MHz loc. oscillator) or external (front panel CLK-IN connector) reference

#### MEMORY

640 kS/ch or 5.12 MS/ch Multi-Event Buffer with independent read and write access divisible into 1 ÷ 1024 buffers. Programmable event size and pre-post trigger

#### TRIGGER

Trigger source

Self-trigger: channel over/under threshold for either Common or Individual (DPP firmware only) trigger generation

External-trigger: Common by TRG-IN or Individual by LVDS connectors (DPP firmware only) Software-trigger: Common by software command

Trigger propagation

TRG-OUT (VME) / GPO (NIM, Desktop) digital output

## Trigger Time Stamp

Default Firmware: 31-bit counter, 16 ns resolution, 17 s range(\*); 48-bit extension by firmware DPP-PHA/PSD: 31-bit counter, 2 ns resolution, 4 s range; 47-bit extension by firmware; 10-bit and 2 ps fine time stamp by digital CFD; 64-bit extension by software

## **SYNCHRONIZATION**

**Clock** propagation Daisy chain (VME only) through CLK-IN/CLK-OUT connectors One-to-many clock distribution from an external clock source

Clock Cable delay compensation

Acquisition Synchronization

Sync Start/Stop through digital I/O (S-IN, TRG-IN or GPI input, TRG-OUT or GPO output) External Trigger Time Stamp reset

#### LVDS I/O (VME only)

16 general purpose LVDS I/Os controlled by FPGA

Busy, Data Ready, Memory full, Individual Trig-Out and other functions can be programmed An Input Pattern from the LVDS I/Os can be associated to each trigger as an event marker

## ANALOG MONITOR (VME only)

12-bit/100 MHz DAC FPGA controlled output with four operating modes: Trigger Majority / Test Pulses / Memory Occupancy / Voltage Level

#### **COMMUNICATION INTERFACE**

**Optical Link** CAEN CONET proprietary protocol, up to 80 MB/s transfer rate Daisy chainable: it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod. A2818/A3818) USB (NIM and Desktop direct, VME via V1718 bridge) **USB 2.0 compliant** Transfer rate up to 30 MB/s VME

#### VME 64X compliant

Data transfer mode: BLT32, MBLT64 (70 MB/s using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s)

## **POWER CONSUMPTIONS**

Desktop: 2.8 A @ 12 V (Typ.) NIM: 4.9 @ +6 V, 250 mA @ -6 V

| ΛE: | V1730          |

|-----|----------------|

|     | 8.2 A @ +5 V   |

|     | 840 mA @ +12 V |

|     | -12 V not used |

|     |                |

VN

V1730x 10.2 A @ +5 V TBD 840 mA @ +12 V -12 V not used

#### **Ordering Options**

| Code         | Description                                                              | Form Factor |

|--------------|--------------------------------------------------------------------------|-------------|

| WDT5730XAAAA | DT5730 - 8 Ch. 14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE             | Desktop     |

| WDT5730BXAAA | DT5730B - 8 Ch. 14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE           | Desktop     |

| WN6730XAAAAA | N6730 - 8 Ch. 14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE              | NIM         |

| WN6730BXAAAA | N6730B - 8 Ch. 14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE            | NIM         |

| WV1730XAAAAA | V1730 - 16 Ch. 14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE             | 6U-VME64    |

| WV1730BXAAAA | V1730B - 16 Ch. 14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE           | 6U-VME64    |

| WV1730CXAAAA | V1730C - 8 Ch. 14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE             | 6U-VME64    |

| WV1730DXAAAA | V1730D - 8 Ch. 14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE            | 6U-VME64    |

| WVX1730XAAAA | VX1730 - 16 Ch. 14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE            | 6U-VME64X   |

| WVX1730BXAAA | VX1730B - 16 Ch. 14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE          | 6U-VME64X   |

| WVX1730CXAAA | VX1730C - 8 Ch. 14 bit 500 MS/s Digitizer: 640kS/ch, CE30, SE            | 6U-VME64X   |

| WVX1730DXAAA | VX1730D - 8 Ch. 14 bit 500 MS/s Digitizer: 5.12MS/ch, CE30, SE           | 6U-VME64X   |

| WFWDPPTFAA30 | DPP-PHA - Digital Pulse Processing for Pulse Height Analysis (x730)      | ALL         |

| WFWDPPNGAA30 | DPP-PSD - Digital Pulse Processing for Pulse Shape Discrimination (x730) | ALL         |

#### **Accessories**

Δ2818 PCI CONET Controller

#### **A3818 A654** PCI Express CONET2 Controller MCX to LEMO Cable Adapter

97

MCX to BNC Cable Adapter

- A317 **Clock Distribution Cable**

- Δ318 SE to Differential Clock Cable Adapter

AI2700 **Optical Fiber Series**

Cables for CONET Optical Link Networks

(\*) Trigger Logic and Trigger Time Stamp counter operate at 125 MHz (i.e. 8 ns or 4 ADC clock cycles), while the counter value is read at a frequency of 62.5 MHz (i.e. 16 ns).

õ

0:0

# **740 Digitizer Family** 64/32 Ch. 12-bit 62.5 MS/s Digitizer

## **Overview**

The 740 is a family of 12-bit and 62.5 MS/s Flash ADC Waveform Digitizers with 2 Vpp (optionally 10 Vpp) of input dynamic range and DC offset adjustment. It is available in three form factors: VME (64 input channels), NIM (32 input channels) and Desktop (32 input channels). Such a high channel density, thanks to an octal ADC chip, implies that most channel settings are common to groups of 8 channels (one group per ADC chip).

Considering the sampling frequency and the bit number, these digititizers are well suited for mid-slow signals as the ones coming from inorganic scintillators coupled to PMTs, gaseous detectors and others. Sampling rate can be reduced thanks to the firmware decimation option.

The acquisition capabilities take advantage of the multi-buffer organization of the channel memory (divisible into a maximum of 1024 buffers). The data stream is continuously written in a circular memory buffer. When the trigger occurs, the digitizer writes further samples for the post trigger and freezes the buffer that can be read by one of the provided readout links. The acquisition can continue without any dead time in a new buffer. Two memory sizes are available according to the different versions of the x740 model: 192 kS/ch or 1.5 MS/ch.

The On-board FPGAs can run default firmware for waveform recording as well as Digital Pulse Processing algorithms (DPP) making the digitizer an enhanced system for Physics application. Special DPP-QDC firmware is supported by x740D digitizer models. In addition to the existing firmware selection, CAEN is willing to collaborate with customers for developing custom solutions.

A common acquisition trigger signal can be provided externally, via front panel digital input connector, or via software. Alternatively, in the

(1) DPP-QDC firmware runs only on x740D digitizer models

default firmware, each 8-channel group can generate a trigger request when at least one of the channels goes under/over a programmable threshold; the requests from the groups are processed by the board to generate a common trigger causing all the channels to acquire an event simultaneously. In the DPP firmware each channel can trigger the event acquisition independently on the others upon the pulse under/ over threshold. The trigger from one board can be provided on a front panel digital output connector.

740 family supports multi-board synchronization making a multi-board system where all ADCs result to be synchronized to a common clock source, and ensuring Trigger Time Tag alignment. Once synchronized, all data will be aligned and coherent across multiple x740 boards.

## Features

ē

G

- · 12-bit @ 62.5 MS/s

- · Analog inputs on ERNI SMC connectors

- · VME64/VME64X (64 ch.), NIM (32 ch.) and Desktop (32 ch.) modules

- · 2 or 10 Vpp input dynamic range with programmable DC offset adj.

- · Sampling rate decimation factor (software selectable)

- · Algorithms for Digital Pulse Processing (DPP)

- · VME, USB and Optical Link communication interfaces

- Multi-board synchronization features

- · Daisy chain capability

- Demo software tools, Control Software for default and DPP firmware, C and LabVIEW libraries

## **Technical Specifications**

## GENERAL

Form Factor 1-unit wide, 6U VME64/VME64X 1-unit wide NIM 154x50x164 mm3 (WxHxD) Desktop

## ANALOG INPUT

Channels 64 channels, single ended (VME); 32 channels, single endend (NIM) 32 channels, single endend (Desktop) or 16 channels by auxiliary on-board connectors Impedance 50 Ω (2 Vpp), 1 k Ω (10 Vpp) Connector ERNI SMC Dual Row 68pin (VME, NIM and Desktop) MCX auxiliary (Desktop) Full Scale Range (FSR) 2 or 10 Vpp (by ordering code) Bandwidth 30 MHz Offset Programmable DAC for DC offset adjustment per each 8-channel group Range: ±1 V @ 2 Vpp, ±5 V @ 10 Vpp

#### **DIGITAL CONVERSION**

Resolution 12 bits Sampling rate 62.5 MS/s simultaneously on each channel (65 MS/s using external clock) Down to 62.5/128 MS/s by programmable decimation factor (62.5/2<sup>n</sup> MS/s; n=0,...,7)

#### ADC CLOCK GENERATION

#### Clock source: internal/external

On-Board PLL provides ADC sampling clock generation from an internal (50 MHz loc. oscillator) or external (front panel CLK-IN connector) reference

#### MEMORY

192 kS/ch or 1.5 MS/ch Multi-Event Buffer with independent read and write access divisible into 1 ÷ 1024 buffers. Programmable event size and pre-post trigger

#### TRIGGER

**Trigger sources**

Self-trigger: channel over/under threshold for either Common or Individual (DPP firmware only) trigger generation

External-trigger: Common by TRG-IN or Individual by LVDS connectors (DPP firmware only) Software-trigger: Common by software command

**Trigger propagation** TRG-OUT (VME) / GPO (NIM and Desktop) digital output

Trigger Time Stamp

Default firmware: 31-bit counter, 16 ns resolution, 17 s range(\*); 48-bit extension by firmware DPP-QDC Firmware: 32-bit counter, 16 ns resolution, 68 s range; 48-bit extension by firmware; 64bit extension by software

#### **SYNCHRONIZATION**

**Clock propagation** Daisy chain (VME only) through CLK-IN/CLK-OUT connectors One-to-many clock distribution from an external clock source Clock Cable delay compensation

Acquisition Synchronization

Sync Start/Stop through digital I/O (S-IN, TRG-IN or GPI input, TRG-OUT or GPO output) External Trigger Time Stamp reset

## LVDS I/O (VME only)

16 general purpose LVDS I/Os controlled by FPGA Busy, Data Ready, Memory full, Individual Trig-Out and other functions can be programmed An Input Pattern from the LVDS I/Os can be associated to each trigger as an event marker

#### ANALOG MONITOR (VME only)

12-bit/100 MHz DAC FPGA controlled output with four operating modes: Trigger Majority / Test Pulses / Memory Occupancy / Voltage Level

#### **COMMUNICATION INTERFACE**

**Optical Link**

CAEN CONET proprietary protocol, up to 80 MB/s transfer rate Daisy chainable: it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod. A2818/A3818)

USB (NIM and Desktop direct, VME via V1718 bridge)

USB 2.0 compliant

Transfer rate up to 30 MB/s

VME Data transfer mode: BLT32, MBLT64 (70 MB/s using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s)

#### **POWER CONSUMPTIONS**

Desktop: 1.9 A @ 12 V (Tvp.) NIM: 3.9 A @ +6 V, 490 mA @ -6 V VME: 5.6 A @ +5 V. 250 mA @ +12 V. -12 V not used

(\*) Trigger Logic and Trigger Time Stamp counter operate at 125 MHz (i.e. 8 ns or 1/2 ADC clock cycles), while the counter value is read at a frequency of 62.5 MHz (i.e. 16 ns).

#### **Ordering Options**

| Code         | Description                                                                        | Form<br>Factor |

|--------------|------------------------------------------------------------------------------------|----------------|

| WDT5740XAAAA | DT5740 - 32 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/ch, EP3C16, SE                   | Desktop        |

| WDT5740CXAAA | DT5740C - 10Vpp input 32 Ch. 12 bit 62.5MS/s Digitizer: 192kS/<br>ch, EP3C16, SE   | Desktop        |

| WDT5740DXAAA | DT5740D - 32 Ch. 12 bit 62.5 MS/s Digitizer: 192kSch, EP3C40, SE                   | Desktop        |

| WN6740DXAAAA | N6740D - 32 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/ch, EP3C40, SE                   | NIM            |

| WN6740XAAAAA | N6740 - 32 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/ch, EP3C16, SE                    | NIM            |

| WN6740CXAAAA | N6740C - 10Vpp input 32 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/<br>ch, EP3C16, SE   | NIM            |

| WV1740XAAAAA | V1740 - 64 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/ch, EP3C16, SE                    | 6U-VME64       |

| WV1740AXAAAA | V1740A - 10Vpp input 64ch 12bit 62.5MS/s Digitizer: 1.5 MS/ch, EP3C16, SE          | 6U-VME64       |

| WV1740BXAAAA | V1740B - 64 Ch. 12 bit 62.5 MS/s Digitizer: 1.5 MS/ch, EP3C16, SE                  | 6U-VME64       |

| WV1740CXAAAA | V1740C - 10Vpp input 64ch 12bit 62.5MS/s Digitizer: 192kS/ch,<br>EP3C16, SE        | 6U-VME64       |

| WV1740DXAAAA | V1740D - 64 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/ch, EP3C40, SE                   | 6U-VME64       |

| WVX1740XAAAA | VX1740 - 64 Ch. 12 bit 62.5 MS/s Digitizer: 192kS/ch, EP3C16, SE                   | 6U-VME64X      |

| WVX1740AXAAA | VX1740A - 10Vpp input 64 Ch. 12 bit 62.5 MS/s Digitizer: 1.5 MS/<br>ch, EP3C16, SE | 6U-VME64X      |

| WVX1740BXAAA | VX1740B - 64 Ch. 12 bit 62.5 MS/s Digitizer: 1.5 MS/ch, EP3C16, SE                 | 6U-VME64X      |

| WVX1740CXAAA | VX1740C - 10Vpp input 64 Ch. 12 bit 62.5 MS/s Digitizer: 192 KS/<br>ch, EP3C16, SE | 6U-VME64X      |

| WVX1740DXAAA | VX1740D - 64 Ch. 12 bit 62.5 MS/s Digitizer: 192kSch, EP3C40, SE                   | 6U-VME64X      |

| WFWDPPQDCAAA | DPP-QDC- Digital Pulse Processing for Time Stamped Digital QDC (x740)              | ALL            |

#### **Accessories**

A746D 32 Channel Adapter for LEMO connector

**A746R** 64 Channel Adapter for LEMO connector

A746B 64 Channel Adapter for LEMO connector

99

A2818 PCI CONET Controller

A3818 PCI Express CONET2 Controller

A654

MCX to LEMO Cable Adapter

A659 MCX to BNC Cable Adapter

AI2700 **Optical Fiber Series**

Cables for CONET Optical Link Networks

A318 SE to Differential Clock Cable Adapter

A317

Clock Distribution Cable

## APPLICATIONS

- Nuclear and Particle PhysicsDark Matter and Astroparticle

- PhysicsFast Neutron spectroscopy

- Fusion Plasma diagnostic, Homeland Security

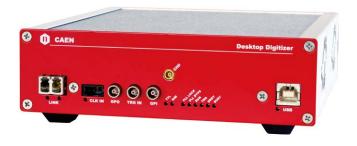

## Well suited for fast signals

# **751 Digitizer Family** 8-4/4-2 Ch. 10-bit 1/2 GS/s Digitizer

## **Overview**

The 751 is a family of 10-bit and 1 GS/s Flash ADC Waveform Digitizers with 1 Vpp of input dynamic range (optionally 0.2 Vpp) and DC offset adjustment. It can work also at 2 GS/s when operating in Dual Edge Sampling (DES) mode, interleaving pairs of input channels.

It is available in three form factors: VME (8 input channels), NIM and Desktop (4 input channels). When in DES mode, half the number of channels is available.

Considering the sampling frequency and the bit number, These digitizers are well suited for fast signals as the ones coming from fast organic, inorganic and liquid scintillators coupled to PMTs or Silicon Photomultipliers, Diamond detectors and others.

The acquisition capabilities take advantage of the multi-buffer organization of the channel memory (divisible into a maximum of 1024 buffers). The data stream is continuously written in a circular memory buffer. When the trigger occurs, the digitizer writes further samples for the post trigger and freezes the buffer that can be read by one of the provided readout links. The acquisition can continue without any dead time in a new buffer. Two memory sizes are available according to the different versions of the x751 model: 1.8-3.6 MS/ch or 14.4-28.8 MS/ch.

The on-board FPGAs can run default firmware for waveform recording as well as Digital Pulse Processing algorithms (DPP) making the digitizer an enhanced system for Physics applications. In addition to the existing firmware selection, CAEN is willing to collaborate with customers for developing custom solutions.

A common acquisition trigger signal can be provided externally, via front panel digital input connector, or via software. Alternatively, each

| Firmware                 | Software                 | Features                                                                            |

|--------------------------|--------------------------|-------------------------------------------------------------------------------------|

| WAVEFORM                 |                          | Digital Waveform Recording                                                          |

| <b>DPP</b><br><b>PSD</b> | PSD Compass<br>反本EN CAEN | Charge Integration<br>Pulse Shape Discrimination<br>Constant Fraction Discriminator |

| DPP                      |                          | Digital Waveform Recording with<br>Enhanced Zero Suppression                        |

83

••0 ••0

channel can generate a trigger request when the input pulse goes under/over a programmable threshold; the trigger requests can be used either locally by the channel (independent triggering with DPP firmware) or processed by the board to generate a common trigger causing all the enable channels to acquire an event simultaneously (default firmware). The trigger from one board can be provided out on a front panel digital output connector.

751 family supports multi-board synchronization making a multi-board system where all ADCs result to be synchronized to a common clock source, and ensuring Trigger Time Tag alignment. Once synchronized, all data will be aligned and coherent across multiple x751 boards.

## Features

- 10-bit @ 1-2 GS/s

- · Analog inputs on MCX coax. connectors (single ended)

- VME64/VME64X (8-4 ch.), NIM (4-2 ch.) and Desktop (4-2 ch.) modules

- 0.2 or 1 Vpp input dynamic range with programmable DC offset adj.

- · Algorithms for Digital Pulse Processing (DPP)

- · VME, USB and Optical Link communication interfaces

- Multi-board synchronization features

- · Daisy chain capability

- Demo software tools, Control Software for default and DPP firmware, C and LabVIEW libraries

## **Technical Specifications**

## GENERAL

Form Factor 1-unit wide, 6U VME64/VME64X 1-unit wide NIM 154x50x164 mm<sup>3</sup> (WxHxD) Desktop

## ANALOG INPUT

Channels 8-4 channels, single ended (VME) 4-2 channels, single ended (NIM, Desktop) Impedance 50 Ω (1 and 0.2 Vpp)

Connector MCX Full Scale Range (FSR) 1 Vpp (0.2 Vpp by ordering code) Bandwidth 500 MHz Offset Programmable DAC for DC offset adjustement. Range: ±0.5 V @ 1 Vpp, ±0.1 V @ 0.2 Vpp

#### **DIGITAL CONVERSION**

Resolution 10 bits Sampling rate 250 to 1000 MS/s simultaneously on each channel (double in DES mode)

#### ADC CLOCK GENERATION

Clock source: internal/external

On-Board PLL provides ADC sampling clock generation from an internal (50 MHz loc. oscillator) or external (front panel CLK-IN connector) reference

#### MEMORY

1.835 MS/ch (3.6 MS/ch in DES mode) or 14.4 MS/ch (28.8 MS/ch in DES mode) Multi Event Buffer with independent read and write access divisible into 1 ÷ 1024 buffers Programmable event size and pre-post trigger

#### TRIGGER

**Trigger source**

Self-trigger: channel over/under threshold for either Common or Individual (DPP firmware only) trigger generation

External-trigger: Common by TRG-IN or Individual by LVDS connectors (DPP firmware only) Software-trigger: Common by software command

Trigger propagation

TRG-OUT (VME) / GPO (NIM and Desktop) digital output

Trigger Time Stamp

Default Firmware, DPP-ZLE: 31-bit counter, 16 ns resolution, 17 s range(\*); 48-bit extension by firmware

DPP-PSD Firmware: 32-bit counter, 1 ns resolution, 4 s range, expandable to 64-bit; 10-bit and 1 ps fine time stamp by digital CFD; 64-bit extension by software

#### **SYNCHRONIZATION**

**Clock propagation**

Daisy chain (VME only) through CLK-IN/CLK-OUT connectors One-to-many clock distribution from an external clock source Clock Cable delay compensation

Acquisition Synchronization

Sync Start/Stop through digital I/O (S-IN, TRG-IN or GPI input, TRG-OUT or GPO output) External Trigger Time Stamp reset

#### LVDS I/O (VME only)

16 general purpose LVDS I/Os controlled by FPGA

Busy, Data Ready, Memory full, Individual Trig-Out and other functions can be programmed An Input Pattern from the LVDS I/Os can be associated to each trigger as an event marker

## ANALOG MONITOR (VME only)

12-bit/100 MHz DAC FPGA controlled output with four operating modes: Trigger Majority / Test Pulses / Memory Occupancy / Voltage Level

## **COMMUNICATION INTERFACE**

**Optical Link** CAEN CONET proprietary protocol, up to 80 MB/s transfer rate Daisy chainable: it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod. A2818/A3818) USB (NIM and Desktop direct, VME via V1718 bridge) USB 2.0 compliant Transfer rate up to 30 MB/s VME

VVME 64X compliant Data transfer mode: BLT32, MBLT64 (70 MB/s using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s)

## **POWER CONSUMPTIONS**

Desktop: 1.8 A @ 12 V (Typ.) NIM: 3.9 A @ +6 V, 120 mA @ -6 V VME: 6.5 A @ +5 V, 200 mA @ +12 V, 300 mA @ -12 V

| Ordering | Ontions     |

|----------|-------------|

| oraoring | 0 0 1 0 1 0 |